Avec le développement rapide des matériaux semi-conducteurs à large bande passante, le carbure de silicium (SiC) est devenu un matériau de base pour l’électronique de puissance et les dispositifs de radiofréquence (RF) en raison de son excellente stabilité thermique, sa forte force de champ de rupture et sa grande mobilité électronique. Cependant, les plaquettes SiC sont sujettes à la déformation pendant la fabrication et le traitement, ce qui non seulement affecte l’uniformité de la croissance épitaxiale, mais pose également des défis à la fabrication et à l’emballage des dispositifs. Par conséquent, une compréhension approfondie des causes, des méthodes de mesure et des stratégies de contrôle de la chaîne du substrat SiC est cruciale pour améliorer les performances de l’appareil et le rendement de la production.

1. Causes de la déformation du substrat SiC

La déformation des substrats SiC est principalement causée par les contraintes internes, les contraintes mécaniques de traitement et les gradients de température pendant le traitement thermique. Les facteurs clés sont les suivants:

(1) contrainte interne

Contrainte thermique: le SiC a un coefficient de dilatation thermique (CTE) fortement anisotrope. Lorsque les plaquettes subissent des changements drastiques de température pendant la croissance, le traitement ou l’épitaxie, un stress thermique se développe, conduisant à la déformation.

Défauts du réseau: les défauts du cristal, comme les dislocations des vis de filetage (TSD), les dislocations des bords de filetage (ted) et les dislocations du plan basal (BPD), introduisent des distorsions localisées du réseau, ce qui contribue à la déformation.

Stress dopage: le processus de dopage (p. ex., dopage de type n avec de l’azote, dopage de type p avec de l’aluminium) modifie les paramètres de la grille, générant une contrainte supplémentaire qui entraîne une déformation.

(2) contrainte mécanique de traitement

Contraintes de meulage et de polissage: un meulage mécanique excessif ou un polissage mécanique chimique (CMP) peut causer une accumulation de contraintes résiduelles, entraînant une déformation de la plaquette.

Contrainte de couche épitaxiale: la déformation de la grille ou la déformation de dilatation thermique entre la couche épitaxiale et le substrat — en particulier dans les couches épitaxiales épaisses (>10 µm)— induit une contrainte supplémentaire, conduisant à la déformation.

(3) Gradients de température pendant le traitement

Les plaquettes SiC subissent des traitements à haute température (1200-1700°C) pendant l’épitaxie et la fabrication du dispositif. Une distribution inégale de la température ou des vitesses de refroidissement rapides peuvent créer des contraintes thermiques non uniformes, contribuant à la déformation.

2. Méthodes de mesure pour SiC substrat Warp

Pour évaluer avec précision la chaîne SiC, des techniques de mesure de haute précision sont nécessaires. Les méthodes couramment utilisées comprennent:

| Méthode de mesure | Principe de base | Caractéristiques caractéristiques |

| Interférométrie optique | Mesure la topographie des plaquettes via une onde lumineuse interférences | Sans contact, haute précision (<1 µm), approprié Pour les grandes tranches |

| Balayage Confocal Laser | Utilise le balayage laser pour calculer la chaîne globale de la plaquette | Rapide, efficace pour diverses rugosités de surface |

Stylet profilométrie | Scanne la surface de la plaquette avec une sonde pour mesurer Variations de forme | Méthode de Contact, idéale pour la chaîne localisée Analyse des données |

| Diffraction de rayons x (DRX) | Détermine la distorsion du réseau par rayons x La diffraction | Utile pour analyser la déformation induite par les contraintes |

La chaîne est généralement exprimée en termes de chaîne totale (chaîne) et de courbure de l’arc (arc):

Total Warp: l’écart entre le point le plus haut et le point le plus bas de la plaquette, mesuré en micromètres (µm).

Arc: la courbure globale de la plaquette par rapport à un plan idéal.

3. Stratégies de contrôle de la chaîne du substrat SiC

Pour réduire la déformation du substrat SiC et améliorer la fiabilité de la fabrication des appareils, plusieurs stratégies d’optimisation peuvent être mises en œuvre.

(1) optimisation du traitement du substrat SiC

Mettre en œuvre un meulage de précision à basse pression pour minimiser les contraintes résiduelles pendant le meulage.

Utiliser le polissage mécanique chimique à plusieurs étapes (CMP) pour éliminer graduellement les couches de contraintes superficielles et améliorer la planéité des plaquettes.

Choisir les orientations cristallographiques appropriées (plan c, plan a, plan r, plan m) pour optimiser la distribution des contraintes.

(2) contrôle des paramètres de croissance épitaxiale SiC

Optimiser l’épaisseur de la couche épitaxiale et les gradients de dopage pour minimiser l’accumulation de stress.

Utiliser des couches tampons graduées pour réduire la contrainte de décalage de la grille entre la couche épitaxiale et le substrat.

Assurer une distribution uniforme de la température dans le réacteur à dépôt chimique de vapeur (CVD) afin d’éviter des gradients thermiques importants pendant l’épitaxie.

Ajuster le rapport SiH₄ (silane) à C₃H o-pe (propane) pour améliorer la qualité de la couche épiaxiale.

(3) traitements de recuit

Recuit à l’hydrogène à haute température (1600-1800°C): réduit les contraintes résiduelles et améliore la planéité des plaquettes.

Processus de refroidissement lent: le refroidissement progressif (10-20°C/min) après épitaxie ou recuit minimise l’accumulation de stress thermique.

4. Normes de l’industrie pour SiC Wafer Warp

Différentes tailles de plaquettes ont des exigences spécifiques de tolérance de chaîne. Les normes courantes de l’industrie sont:

Plaquettes SiC de 6 pouces (150 mm) :

Total Warp < 20 µm (qualité de l’appareil de haute qualité)

Arc < 10 µm (exigence d’uniformité élevée)

Plaquettes SiC de 8 pouces (200 mm) :

Warp < 30 µm (niveau cible)

Arc < 15 µm (exigence de fabrication d’appareils)

5. Conclusion Conclusion

SiC substrat warp a un impact significatif sur la qualité de la couche épitaxiale et les performances de l’appareil. Les principales causes sont les contraintes internes, les contraintes mécaniques de traitement et les gradients thermiques pendant les processus à haute température. En optimisant les processus de broyage et de polissage, en affinant les paramètres de croissance épitaxiale, en mettant en œuvre des stratégies de dopage appropriées et en appliquant des traitements de recuit à haute température, la chaîne SiC de wafer peut être efficacement minimisée, conduisant à des wafers de haute qualité qui répondent aux exigences strictes des applications d’électronique de puissance. Alors que les dispositifs SiC continuent à se développer dans les véhicules électriques, les onduleurs photovoltaïques et les systèmes de communication à haute fréquence, la réduction de la chaîne du substrat SiC sera un facteur essentiel pour améliorer la compétitivité des produits.

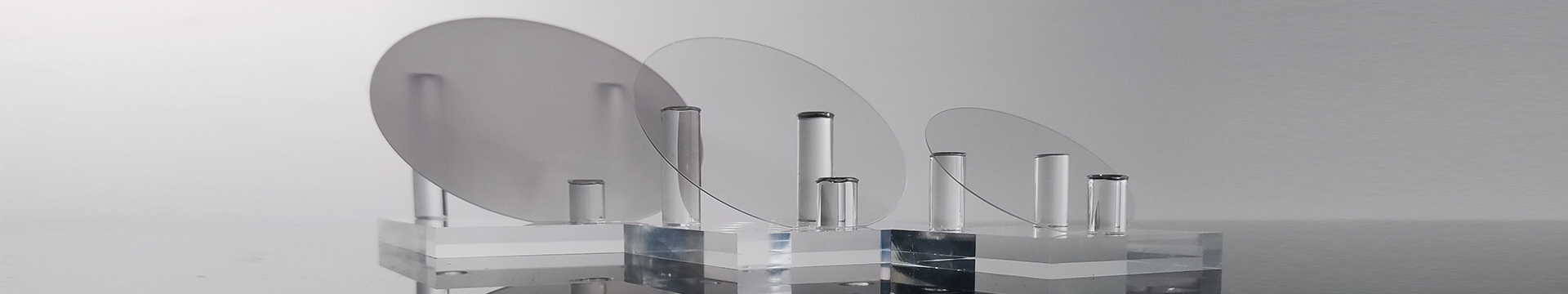

Nos produits de substrat SiC sont fabriqués avec un contrôle rigoureux de la chaîne, fournissant des plaquettes SiC de haute qualité qui maintiennent les valeurs de la chaîne en deçà des normes de l’industrie, assurant ainsi leur adéquation aux applications haut de gamme.

Avec les progrès continus de l’électronique de puissance, des dispositifs RF et des technologies optoélectroni...

Le choix des matériaux de substrat joue un rôle crucial dans le développement d’appareils RF (radiofréquence) ...

Introduction IntroductionLe carbure de silicium (La SiC), le nitrure de gallium (GaN) et le saphir (Al₂O₃) son...